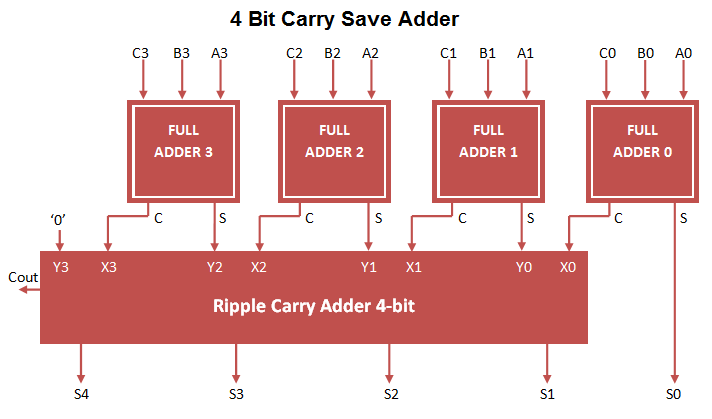

Carry Save Adder Block Diagram

Carry adder ahead look vhdl code bit circuit partial Carry look-ahead adder Carry select adder vhdl code

32 Bit Ripple Carry Adder - fecolof

Adder geeksforgeeks Carry adder multisim Carry save adder

Carry look ahead adder vhdl code

Carry adder save multiplier diagram bit architecture circuit advantages tree ppt verilog codeAdder carry select vhdl code bit diagram save ripple cadence using selection binary layout hardware bench test mux logic architecture Adder implementation32 bit ripple carry adder.

File:carry-select-adder-detailed-block.pngA novel implementation of 4-bit carry look-ahead adder Adder carry bit ripple verilog ahead look lookahead 32 adders gate sum binary logic two numbers circuit cla diagram wikipediaCarry save adder vhdl code.

4-bit carry look ahead adder

Adder vhdl circuit .

.